BeagleLogic is a part of a vision of inexpensive Single Board Computers being repurposed as a useful debugging tool, a logic analyzer. It should be the first in a series of tools to make high quality, feature-rich and well-connected instruments accessible to more people over a familiar Linux environment. I see BeagleLogic as an educational tool that can help in understanding digital protocols as well, as one can use the same BeagleBone to send SPI and I2C signals which can be looped back into the inputs to BeagleLogic.

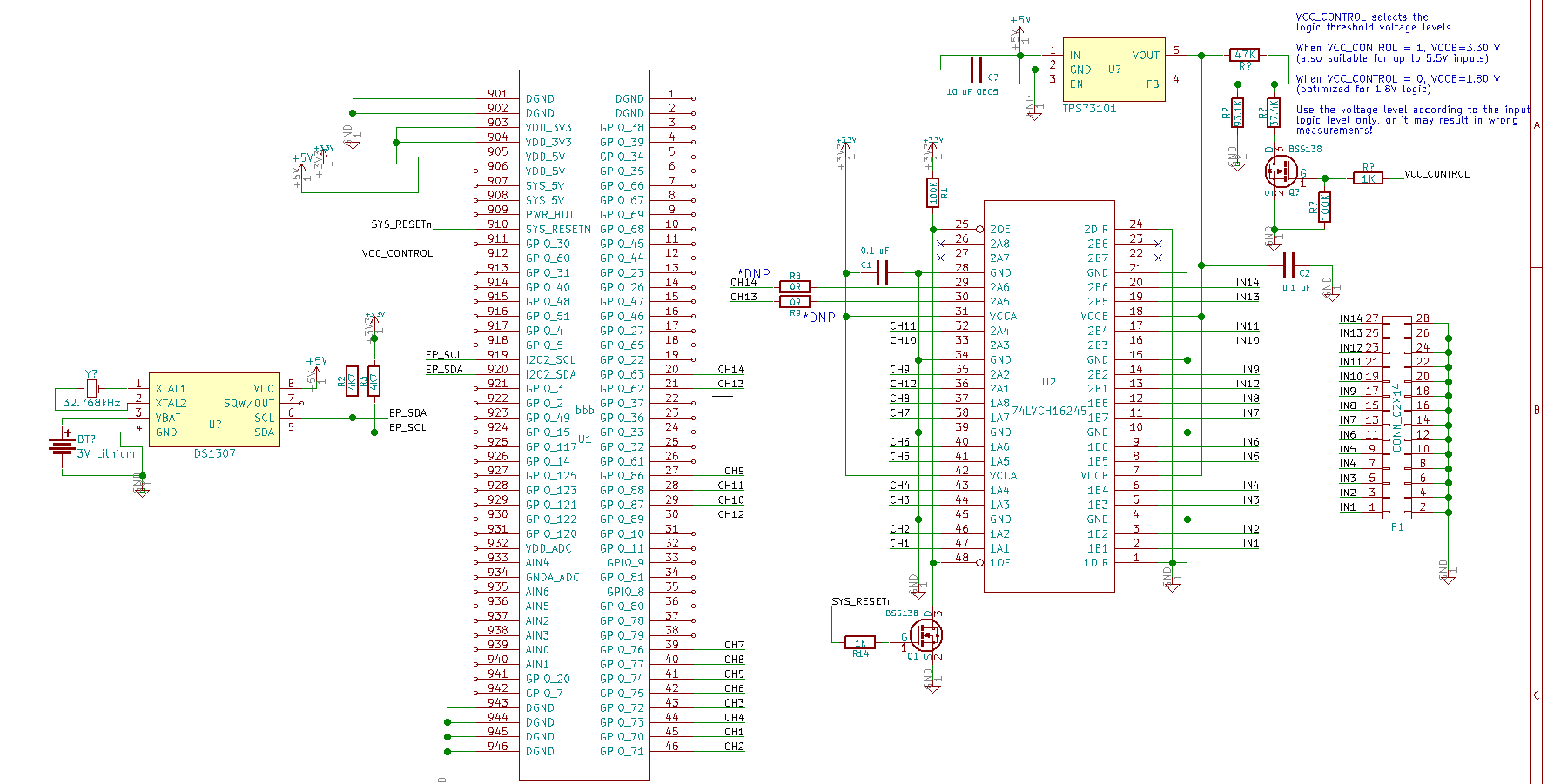

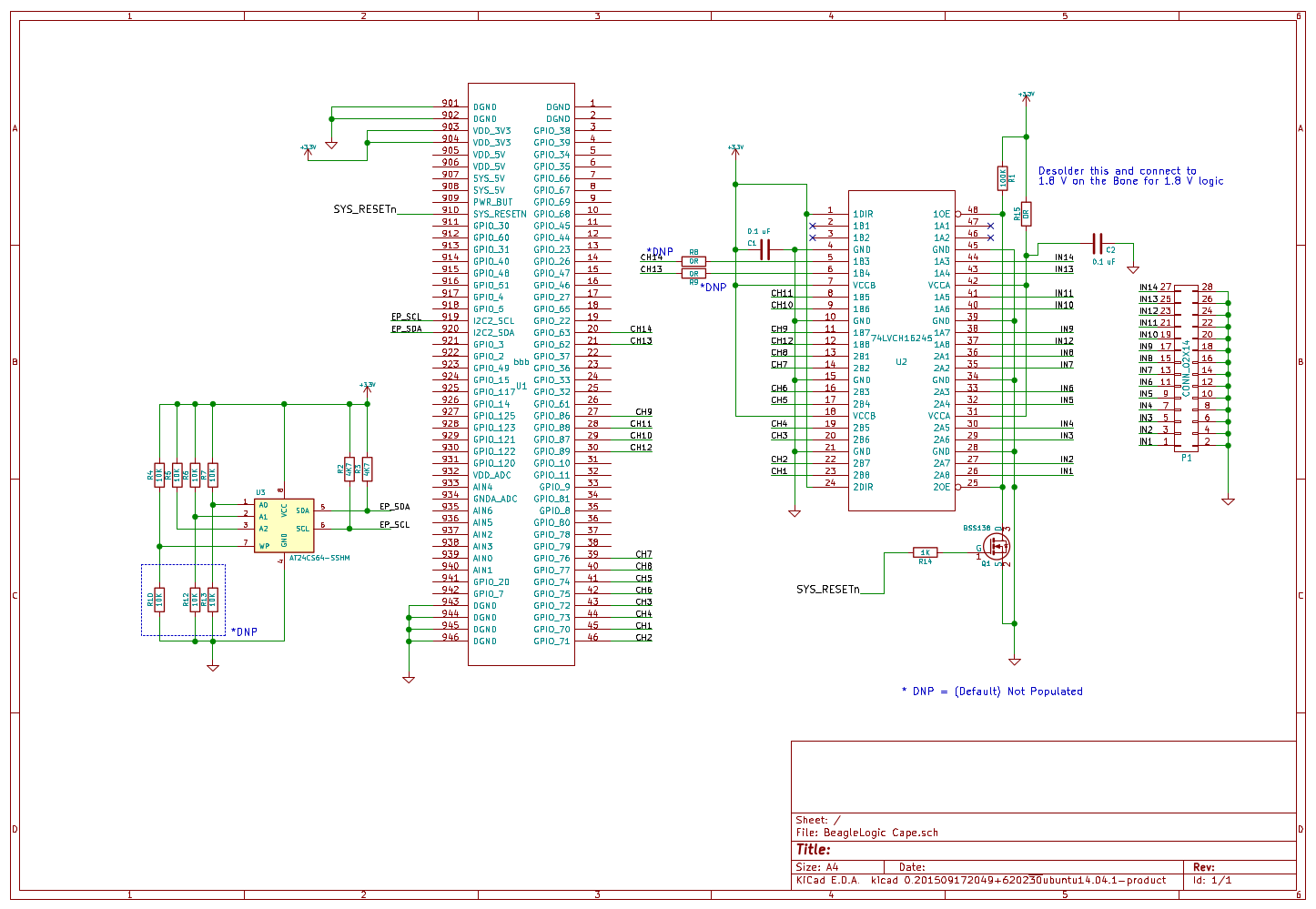

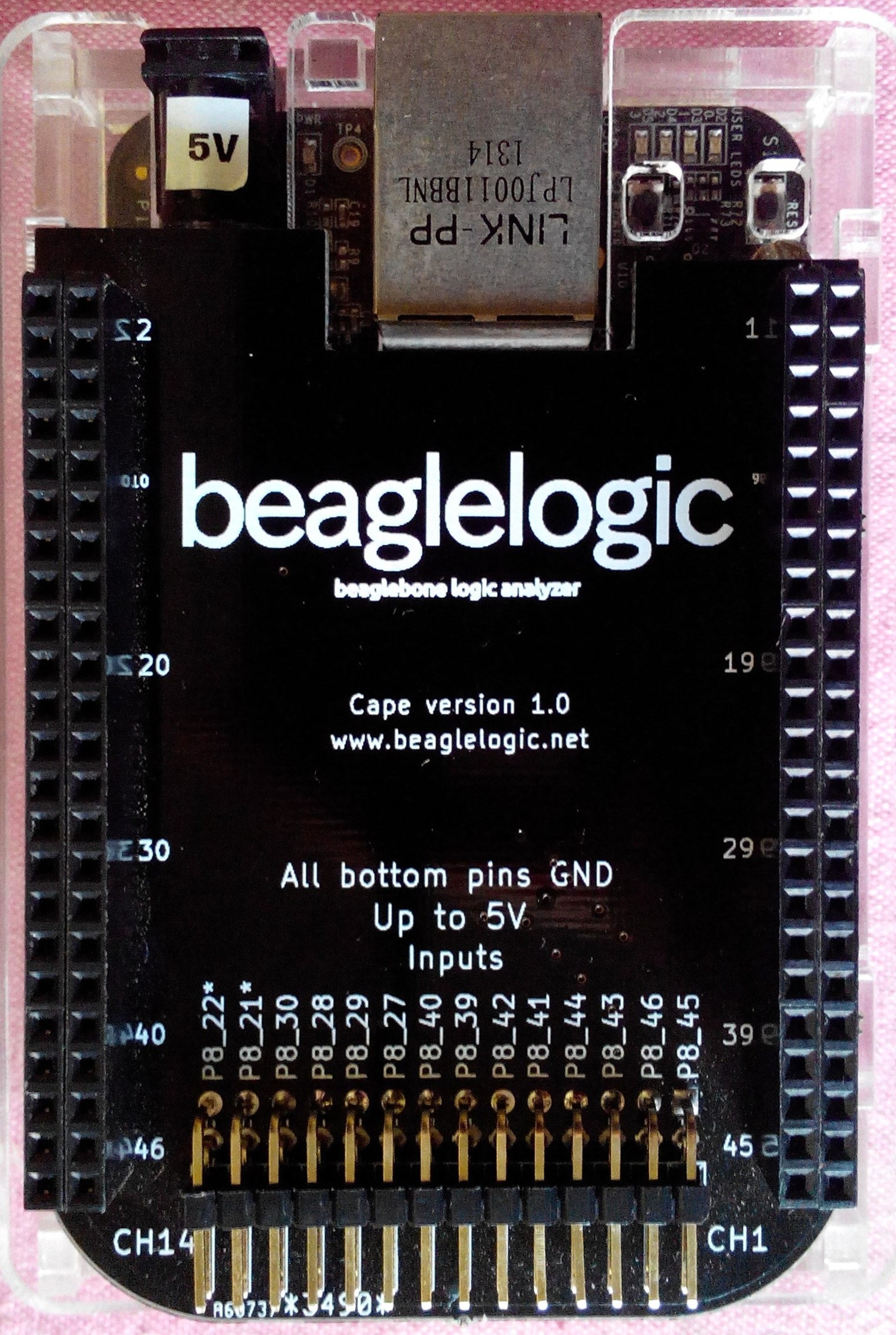

BeagleLogic is delivered as a combination of a ready-to-run BeagleLogic System Image (Software) that can be flashed onto a SD card and which is preloaded with the kernel modules, firmware and software necessary to run BeagleLogic right after the system boots up and a BeagleLogic Cape (Hardware) that logic level translates 5V signals so you can debug 5V logic circuits with the BeagleBone Black.

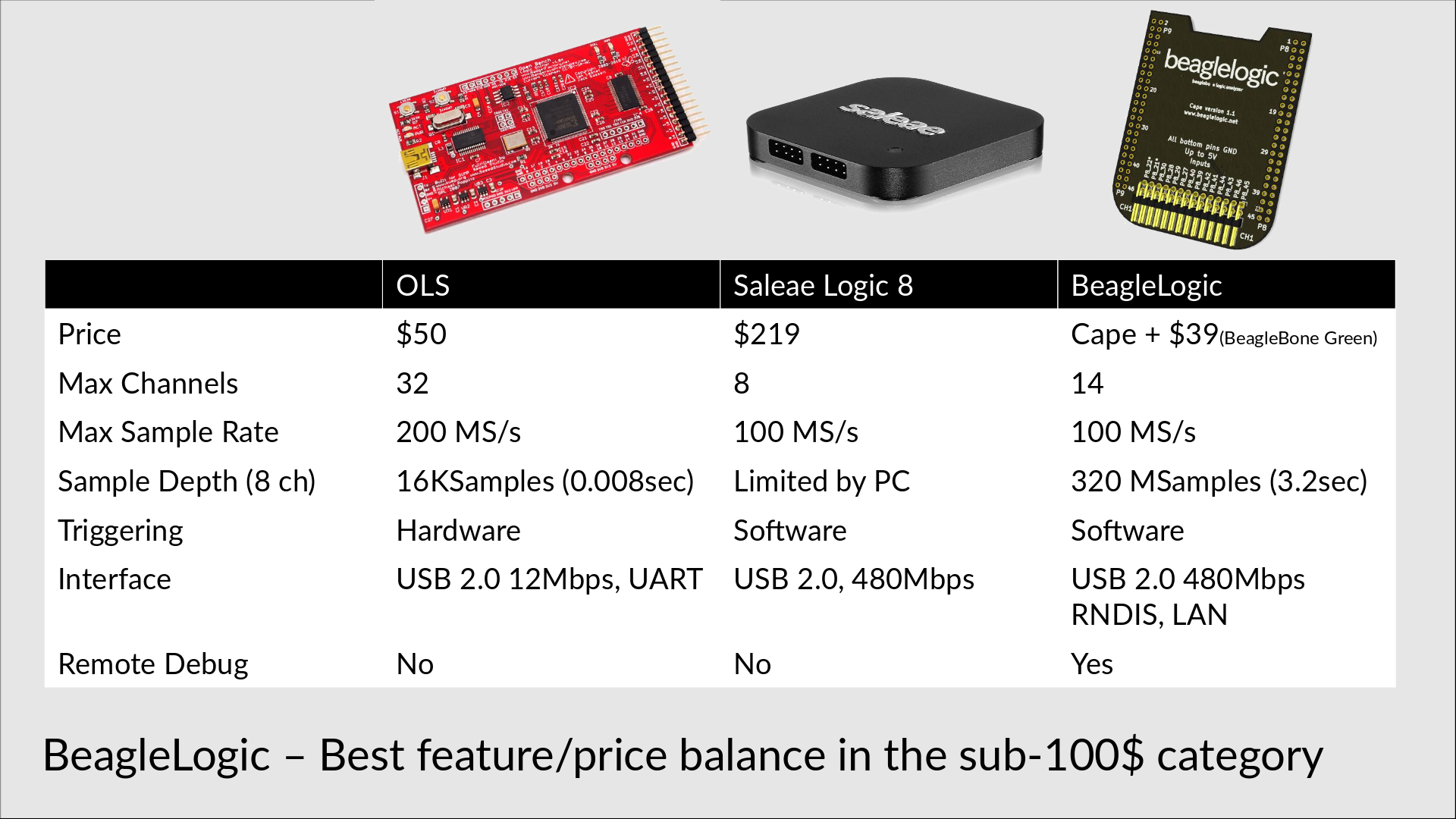

This infographic compares BeagleLogic to other leading Logic Analyzers:

BeagleLogic makes use of the powerful sigrok library that provides a standardized interface to DMMs, scopes and logic analyzers. For logic analyzers, sigrok tools support decoding over 50 different digital protocols (see complete list here) for supported protocols. Since BeagleBone runs Linux, it can run the whole sigrok tool set by itself, but it is usually better to process data on a PC as it's faster.

There's a series of technical explanation walkthorughs on my blog that detail how BeagleLogic works:

- Part 1 : Building a Logic Analyzer using the PRUs - Explaining the functioning of the PRU side of things work

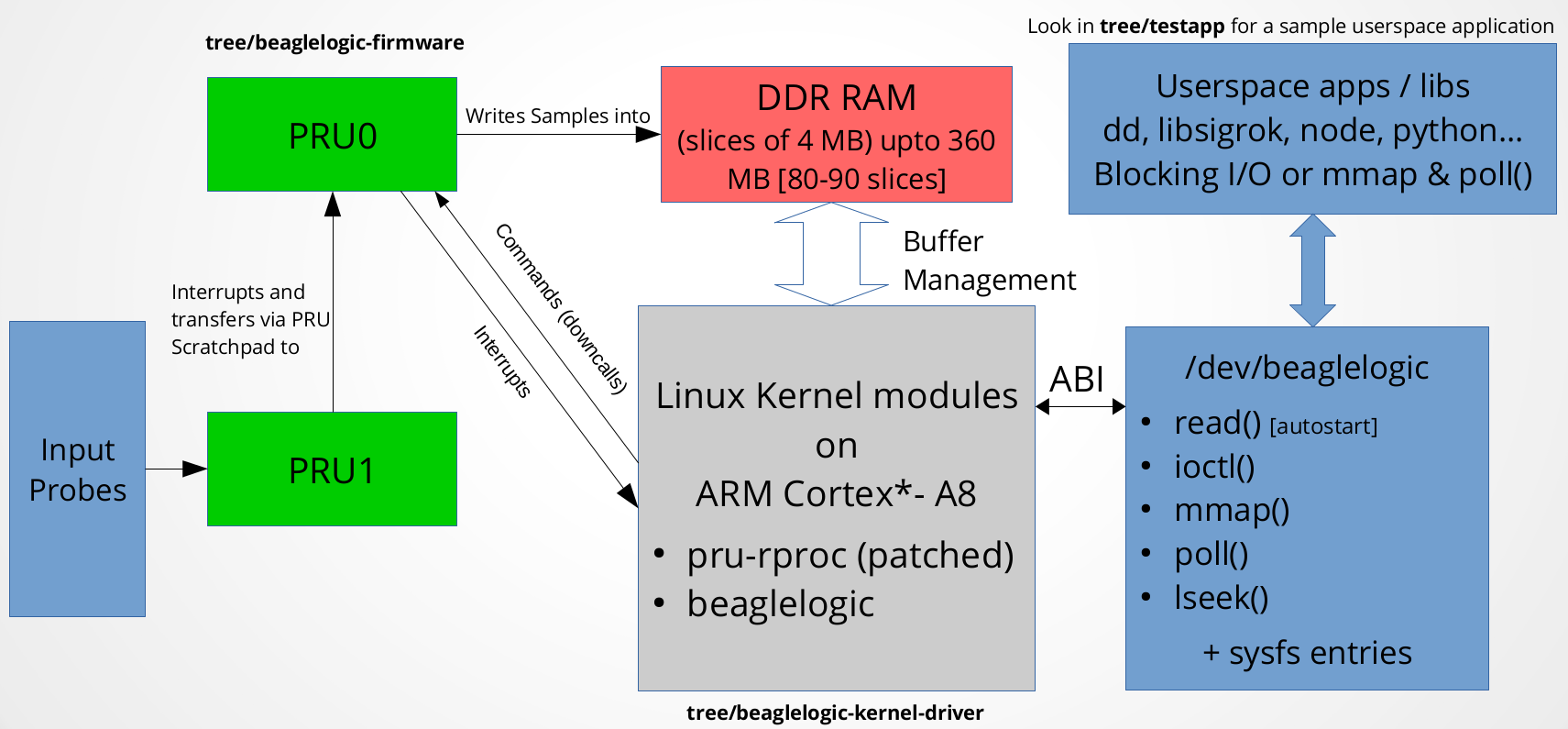

Here's a system-level block diagram that explains how BeagleLogic works:

License Details

Each component of the project as seen above is individually licensed as follows:

(i) The PRU Firmware is under GPLv2 only license.

(ii) The Linux Kernel Module is under GPLv2 only license.

(iii) The sigrok bindings form a part of the sigrok suite, so fall under GPLv3 or later license.

(iv) The Web Interface and the NodeJS backend is under MIT License

(v) The BeagleLogic cape is licensed under the CERN Open Hardware License

(vI) The BeagleLogic logo on the PCB and the video (created by me with Inkscape) is licensed under CC-BY-SA-4.0 http://creativecommons.org/licenses/by-sa/4.0/

Kumar, Abhishek

Kumar, Abhishek

Anderson Antunes

Anderson Antunes Zapp

Zapp Elias Bakken

Elias Bakken

I'm looking into building a BeagleLogic myself

from what I understand the one thing holding back the V2 schematic is the HV clamping for 12V / -12V inputs

any news on where this might be up to. If it's still in progress do you know which IC your planning on using for the HV clamping?

Edit, it looks like the Saleae Logic Pro uses a series of individual Fet's to buffer the input for a max range of 10V to -10V, then feeds the inputs via a series of ADA4891-4 comparators